用VHDL语言 设计4位序列检测器,当检测到“0110”时输出1,否则输出0.

来源:学生作业帮助网 编辑:作业帮 时间:2024/07/31 02:41:06

用VHDL语言 设计4位序列检测器,当检测到“0110”时输出1,否则输出0.

用VHDL语言 设计4位序列检测器,当检测到“0110”时输出1,否则输出0.

用VHDL语言 设计4位序列检测器,当检测到“0110”时输出1,否则输出0.

需要设计一个4位的串入并出移位寄存器和一个4位的二进制数值比较器:

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

ENTITY detector IS

GENERIC(m:std_logic_vector(3 downto 0):="0110");

PORT(clk,clr,s_in:IN std_logic; equal:OUT std_logic);

END detector;

ARCHITECTURE behavioral OF detecor IS

SIGNAL p:std_logic_vector(3 DOWNTO 0);

BEGIN

PROCESS(clk,clr)

BEGIN

IF clr='0' THEN

p<=(OTHERS => '0');

ELSIF rising_edge(clk) THEN

p <= s_in&p(3 DOWNTO 1);

END IF;

END PROCESS;

PROCESS(p)

BEGIN

IF p=m THEN

equal <='1';

ELSE

equal <='0';

END IF;

END PROCESS;

END behavioral;

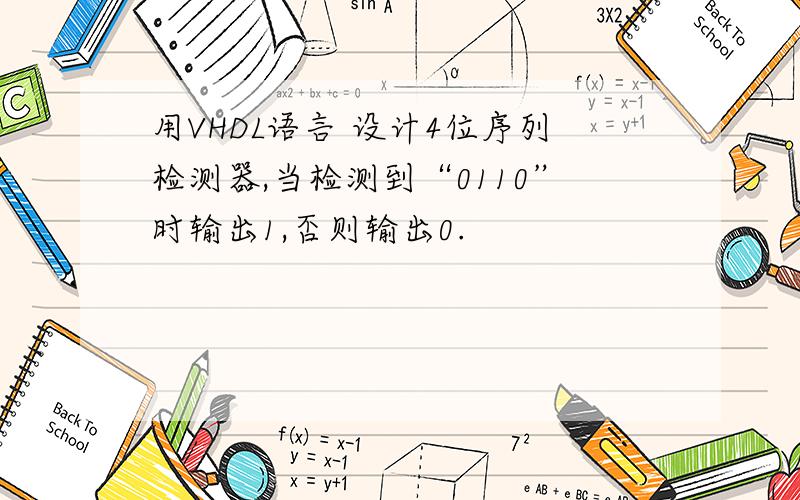

仿真图如下: